# Application Note : Telink Hardware Design Guide

AN-16101000-E1

Ver 1.0.0

2016/10/14

#### **Brief:**

This document is designed to provide developers with guide on Telink SoC-based hardware design. It mainly introduces hardware functions and schematic design guide for TLSR8267/TLSR8267F512, TLSR8266/TLSR8266F512 and TLSR8263, as well as general PCB design rules.

Published by Telink Semiconductor

Bldg 3, 1500 Zuchongzhi Rd, Zhangjiang Hi-Tech Park, Shanghai, China

© Telink Semiconductor All Right Reserved

#### Legal Disclaimer

Telink Semiconductor reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Telink Semiconductor disclaims any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Telink Semiconductor does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications. Customers using or selling Telink Semiconductor products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Telink Semiconductor for any damages arising or resulting from such use or sale.

#### Information:

For further information on the technology, product and business term, please contact Telink Semiconductor Company (<u>www.telink-semi.com</u>).

For sales or technical support, please send email to the address of:

telinkcnsales@telink-semi.com

telinkcnsupport@telink-semi.com

#### **Revision History**

| Version | Major Changes   | Date    | Author          |

|---------|-----------------|---------|-----------------|

| 1.0.0   | Initial release | 2016/10 | W.W.X., Cynthia |

#### **Table of contents**

| 1  | Brie | rief4                                    |    |  |

|----|------|------------------------------------------|----|--|

| 2  | TLS  | R8267/TLSR8267F512 Hardware Design Guide | .5 |  |

| 2. | 1    | Hardware functions                       | .5 |  |

| 2. | 2    | Schematic design guide                   | .8 |  |

| 3  | TLS  | R8266/TLSR8266F512 Hardware Design Guide | .9 |  |

| 3. | 1    | Hardware functions9                      |    |  |

| 3. | 2    | Schematic design guide                   | 12 |  |

| 4  | TLS  | R8263 Hardware Design Guide              | 13 |  |

| 4. | 1    | Hardware functions                       | 13 |  |

| 4. | 2    | Schematic design guide                   | 16 |  |

| 5  | Ger  | neral PCB Design Rules                   | 17 |  |

\*

#### 1 Brief

This document is designed to provide developers with guide on Telink SoC-based hardware design. It mainly introduces hardware functions and schematic design guide for TLSR8267/TLSR8267F512, TLSR8266/TLSR8266F512 and TLSR8263, as well as general PCB design rules.

# 2 TLSR8267/TLSR8267F512 Hardware Design Guide

### 2.1 Hardware functions

| No. | ltem                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Package                       | ♦ Both TLSR8267 and TLSR8267F512 support QFN32 and QFN48 package.                                                                                                                                                                                                                                                                                                                                                                                       |

| 2   | Program memory<br>(Flash)     | <ul> <li>♦ TLSR8267F512 embeds 512KB Flash.</li> <li>♦ TLSR8267 supports external 128/512KB Flash.</li> </ul>                                                                                                                                                                                                                                                                                                                                           |

| 3   | Clock                         | <ul> <li>For applications with requirement of accurate timing (e.g. electronic<br/>label), it's needed to connect external 32.768KHz crystal via the<br/>ANA_C&lt;2&gt; and ANA_C&lt;3&gt; pin.</li> </ul>                                                                                                                                                                                                                                              |

| 4   | Swire                         | <ul> <li>Support Single Wire interface:</li> <li> TLSR8267 QFN32 package only supports SWS (Single Wire Slave). </li> <li> Other packages support both SWM (Single Wire Master) and SWS. </li> <li> When 8267 acts as Slave, it can communicate with SWM of Master via SWS. </li> <li> When 8267 acts as Master, it can communicate with SWS of Slave via SWM. </li> </ul>                                                                              |

| 5   | GPIO                          | <ul> <li>♦ TLSR8267F512 QFN32/QFN48 package supports up to 21/36 GPIOs.</li> <li>♦ TLSR8267 QFN32/QFN48 package supports up to 21/37 GPIOs.</li> </ul>                                                                                                                                                                                                                                                                                                  |

| 6   | Wakeup source                 | ANA_A<0>~ANA_E<3> can be independently configured as active-high or active-low Pad wakeup sources.                                                                                                                                                                                                                                                                                                                                                      |

| 7   | Pull-up/Pull-down<br>resistor | <ul> <li>ANA_A&lt;0&gt;~ANA_E&lt;3&gt; support independently configurable<br/>10KΩ/1MΩ pull-up resistor or 100KΩ pull-down resistor which are all<br/>disabled by default.</li> <li>The DP pin also supports configurable 1.5KΩ pull-up resistor for USB<br/>use. This pull-up resistor is disabled by default.</li> </ul>                                                                                                                              |

| 8   | Driving strength<br>(DS)      | <ul> <li>◇ ANA_E&lt;1&gt;, ANA_E&lt;0&gt;: maximum=16mA ("DS"=1), minimum=12mA ("DS"=0).</li> <li>◇ ANA_E&lt;3&gt;, ANA_E&lt;2&gt;: maximum=12mA ("DS"=1), minimum=8mA ("DS"=0).</li> <li>◇ Other GPIO pins support maximum drive level of 4mA ("DS"=1) and minimum drive level of 0.7mA ("DS"=0)</li> <li>◇ The "DS" configuration will take effect when the pin is used as output, and it's set as the strongest driving level by default.</li> </ul> |

| No. | ltem                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9   | PWM                            | <ul> <li>Support 6-channel PWM output: PWM0~PWM5. PWM#n_N<br/>indicates inverted output.</li> <li>PWM0~PWM5 all support continuous output mode.</li> <li>PWM0 and PWM1 support 3 modes including continuous mode,<br/>counting mode and IR mode. Other PWM channels only support<br/>continuous mode.</li> <li>Only PWM1/1_N and PWM0/0_N can be used as IR driving IOs.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10  | I2C                            | <ul> <li>Embed I2C hardware module.</li> <li>Support Master and Slave mode. Act as Slave mode by default.</li> <li>One group among ANA_A&lt;3&gt;/ANA_A&lt;4&gt;, ANA_B&lt;6&gt;/ANA_B&lt;7&gt; and ANA_C&lt;0&gt;/ANA_C&lt;1&gt; can be configured as SDA/SCL to communicate with other device via I2C.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11  | SPI                            | <ul> <li>♦ Embed SPI hardware module.</li> <li>♦ Support Master and Slave mode. Act as Slave mode by default.</li> <li>♦ One group among ANA_A&lt;2&gt;~ANA_A&lt;5&gt; and ANA_B&lt;4&gt;~ANA_B&lt;7&gt; can be configured as SPI pins to communicate with other device via SPI.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 12  | I2C and SPI usage              | <ul> <li>I2C hardware and SPI hardware modules in the chip share part of the hardware, as a result, when both hardware interfaces are used, the restrictions listed below need to be taken into consideration.</li> <li>◇ I2C and SPI hardware cannot be used as Slave at the same time.</li> <li>◇ I2C Slave mode and SPI Master mode cannot be used at the same time.</li> <li>◇ I2C Master mode and SPI Slave mode cannot be used at the same time.</li> <li>◇ I2C and SPI can be used as Master at the same time only when ANA_A&lt;2&gt;~ ANA_A&lt;5&gt; are configured as SPI pins and ANA_C&lt;0&gt;~ ANA_C&lt;1&gt; are configured as I2C pins. Note that it's needed to configure related registers before each I2C/SPI operation. Please refer to corresponding SDK.</li> </ul> |

| 13  | UART                           | <ul> <li>◇ Embed UART to implement full-duplex transmission and reception.</li> <li>◇ One group among ANA_A&lt;6&gt;/ANA_A&lt;7&gt;, ANA_B&lt;2&gt;/ANA_B&lt;3&gt; and ANA_C&lt;2&gt;/ANA_C&lt;3&gt; can be configured as TX/RX to communicate with other device via UART.</li> <li>◇ Support hardware flow control when ANA_C&lt;4&gt; and ANA_C&lt;5&gt; are configured as RTS and CTS pins.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                 |

| 14  | Analog<br>microphone<br>(AMIC) | <ul> <li>◇ Support AMIC input.</li> <li>◇ Adopt differential input by default: use<br/>ANA_C&lt;3&gt;/ANA_C&lt;4&gt;/ANA_C&lt;5&gt; as AmicBias/AmicSN/AmicSP.</li> <li>◇ If PC3 is configured as other multiplexed function, other pin of PortC can be used as AmicBias.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| No. | ltem                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | Digital<br>microphone<br>(DMIC) | <ul> <li>♦ Support DMIC input.</li> <li>♦ Use ANA_A&lt;0&gt;/ANA_A&lt;1&gt; as DMIC_DI/DMIC_CLK.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 16  | Audio output<br>(SDM)           | <ul> <li>♦ Support mono-channel audio output.</li> <li>♦ Use ANA_E&lt;0&gt;/ANA_E&lt;1&gt; as SDM_P/SDM_N.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 17  | ADC                             | ADC input channel: ANA_B<0>~ANA_B<7>, ANA_C<0>~ANA_C<1>,<br>ANA_C<6>~ANA_C<7>.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 18  | Battery detect                  | <ul> <li>For battery detect, the ANA_B&lt;7&gt; pin is used by default.</li> <li>If dual dry batteries are directly used to supply power, system power supply can be configured as reference voltage for internal ADC. The system voltage can be directly detected without the need of the PB7 pin of the chip.</li> <li>If single dry battery is used to supply power via boost DCDC, it's needed to directly connect the PB7 pin with the battery to detect its voltage. No external divider resistor is needed.</li> <li>If Li battery is used to supply power via LDO step-down circuit, to detect battery voltage, it's needed to connect the PB7 pin with the battery via external 2:1 divider resistors so that the PAD can bear the voltage.</li> </ul> |

# 2.2 Schematic design guide

| No. | ltem                                               | Description                                                                                                                                                                                                                                                                                                                               |

|-----|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VDDDEC                                             | ♦ VDDDEC should be connected to GND via 1uF filtering capacitor.                                                                                                                                                                                                                                                                          |

| 2   | DVDD3F                                             | ♦ DVDD3F should be connected to GND via 10uF filtering capacitor.                                                                                                                                                                                                                                                                         |

| 3   | DVDD, AVDD                                         | <ul> <li>Both DVDD and AVDD pin should be connected with a 1uF decoupling capacitor.</li> </ul>                                                                                                                                                                                                                                           |

| 4   | Reset pin                                          | ♦ RST pin should be connected to GND via 1uF capacitor.                                                                                                                                                                                                                                                                                   |

| 5   | Test points for FW<br>burning and<br>wakeup source | <ul> <li>◇ It's needed to reserve three test points including VCC, GND and SWS for firmware burning.</li> <li>◇ According to test plan, it's needed to reserve a GPIO test point as wakeup source for sleep/wakeup test. It's recommended to use ANA_B&lt;1&gt; as wakeup source corresponding to Telink standard test script.</li> </ul> |

| 6   | Crystal oscillator                                 | <ul> <li>◇ It's recommended to use 12MHz crystal with spec of<br/>12MHz-12pF-+/-20ppm.</li> <li>◇ Load capacitors are reserved for crystal pins (not soldered by<br/>default).</li> </ul>                                                                                                                                                 |

| 7   | BQB certificate<br>&<br>FCC RF certificate         | <ul> <li>It's needed to reserve TX/RX test points for BLE BQB certificate test.</li> <li>FCC RF certificate matching location: It's needed to reserve π-type low pass filtering circuit for ANT pin in order to decrease RF harmonic energy. Default parameters: 2.2nH series inductor, two 1.5pF shunt capacitors.</li> </ul>            |

| 8   | Antenna                                            | <ul> <li>Telink solution uses monopole PCB antenna.</li> <li>It's needed to reserve a shunt device matching location near the antenna port for antenna match debug.</li> </ul>                                                                                                                                                            |

| 9   | USB                                                | <ul> <li>For USB dongle applications, it's needed to connect a 33Ω series<br/>resistor between the DP/DM pin and the USB port, and the resistor<br/>should be close to the USB port.</li> </ul>                                                                                                                                           |

| 10  | Power supply for<br>MIC module                     | <ul> <li>PIN28/PIN20 of TLSR8267F512 QFN48/QFN32 package supplies<br/>power for mic module. It's needed to adopt star-type connection,<br/>i.e. single power line is needed to trace from DVDD source to this<br/>pin. Pay special attention to this point on PCB design.</li> </ul>                                                      |

| 11  | IR power supply                                    | <ul> <li>For remote control applications, it's needed to connect IR power<br/>supply to GND via 220uF/10V filtering capacitor.</li> </ul>                                                                                                                                                                                                 |

# 3 TLSR8266/TLSR8266F512 Hardware Design Guide

### 3.1 Hardware functions

| No. | ltem                          | Description                                                                                                                                                                                                                                                                                                                                                        |

|-----|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Package                       | <ul> <li>◇ TLSR8266 supports QFN56, QFN48 and QFN32 package.</li> <li>◇ TLSR8266F512 supports QFN48 and QFN32 package.</li> <li>◇ TLSR8266F128 supports QFN24 package.</li> </ul>                                                                                                                                                                                  |

| 2   | Program memory<br>(Flash)     | <ul> <li>◇ TLSR8266F512 embeds 512KB Flash.</li> <li>◇ TLSR8266F128 embeds 128KB Flash.</li> <li>◇ TLSR8266 supports external 128/512KB Flash.</li> </ul>                                                                                                                                                                                                          |

| 3   | Swire                         | <ul> <li>Support Single Wire interface:</li> <li>◇ QFN32 and QFN24 only support SWS (Single Wire Slave).</li> <li>◇ Other packages support both SWM (Single Wire Master) and SWS.</li> <li>◇ When 8266 acts as Slave, it can communicate with SWM of Master via SWS.</li> <li>◇ When 8266 acts as Master, it can communicate with SWS of Slave via SWM.</li> </ul> |

| 4   | GPIO                          | <ul> <li>◇ TLSR8266F512 QFN32/QFN48 package supports up to 20/35 GPIOs.</li> <li>◇ TLSR8266 QFN32/QFN48/QFN56 package supports up to 22/37/41 GPIOs.</li> <li>◇ TLSR8266F128 QFN24 package supports up to 12 GPIOs.</li> </ul>                                                                                                                                     |

| 5   | Wakeup source                 | <ul> <li>ANA_A&lt;0&gt;~ANA_F&lt;1&gt; can be independently configured as active-high or active-low Pad wakeup sources.</li> <li>♦ It's not recommended to use ANA_C&lt;0&gt;~ANA_C&lt;3&gt; as wakeup pins.</li> </ul>                                                                                                                                            |

| 6   | Pull-up/Pull-down<br>resistor | <ul> <li>All GPIOs support independently configurable 10KΩ/1MΩ pull-up resistor or 100KΩ pull-down resistor which are all disabled by default.</li> <li>The DP pin also supports configurable 1.5KΩ pull-up resistor (disabled by default). To enable this pull-up resistor, set analog register 0x00[4] as 1.</li> </ul>                                          |

| 7   | DM/DP                         | When GPIO function is enabled, the DM and DP pin can only be used<br>as GPI (input).                                                                                                                                                                                                                                                                               |

| 8   | Driving strength<br>(DS)      | <ul> <li>ANA_B&lt;6&gt;, ANA_B&lt;5&gt;: maximum=8mA ("DS"=1), minimum=4mA ("DS"=0).</li> <li>ANA_E&lt;5&gt;, ANA_E&lt;4&gt;: maximum=16mA ("DS"=1), minimum=12mA ("DS"=0).</li> <li>Other GPIO pins support maximum drive level of 4mA ("DS"=1) and minimum drive level of 0.7mA ("DS"=0).</li> </ul>                                                             |

|     |                               | The "DS" configuration will take effect when the pin is used as output,<br>and it's set as the strongest driving level by default.                                                                                                                                                                                                                                 |

| No. | ltem                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9   | GPIO default state           | <ul> <li>♦ GPIO acts as input by default except ANA_B&lt;0&gt; and ANA_D&lt;5:4&gt;:</li> <li>ANA_B&lt;0&gt; and ANA_D&lt;4&gt; output 1, while ANA_D&lt;5&gt; outputs 0.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10  | PWM                          | <ul> <li>◇ Supports 6-channel PWM output: PWM0~PWM5. PWM#n_N indicates inverted output.</li> <li>◇ PWM0~PWM5 all support continuous output mode.</li> <li>◇ PWM0 and PWM1 support 3 modes including continuous mode, counting mode and IR mode. Other PWM channels only support continuous mode.</li> <li>◇ Only PWM1/1_N and PWM0/0_N can be used as IR driving IOs.</li> </ul>                                                                                                                                                                                                                                                          |

| 11  | 12C                          | <ul> <li>◇ Embed I2C hardware module.</li> <li>◇ Support Master and Slave mode. Act as Slave mode by default.</li> <li>◇ ANA_E&lt;7&gt;/ANA_F&lt;1&gt; can be configured as SDA/SCL to communicate with other device via I2C.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12  | SPI                          | <ul> <li>◇ Embed SPI hardware module.</li> <li>◇ Support Master and Slave mode. Act as Slave mode by default.</li> <li>◇ ANA_E&lt;6&gt;/ANA_E&lt;7&gt;/ANA_F&lt;0&gt;/ANA_F&lt;1&gt; can be configured as SPI CN/DI/DO/CK pins to communicate with other device via SPI.</li> </ul>                                                                                                                                                                                                                                                                                                                                                       |

| 13  | I2C and SPI usage            | <ul> <li>I2C hardware and SPI hardware modules in the chip share part of the hardware, as a result, when both hardware interfaces are used, the restrictions listed below need to be taken into consideration.</li> <li>I2C and SPI hardware cannot be used as Slave at the same time.</li> <li>I2C Slave mode and SPI Master mode cannot be used at the same time.</li> <li>I2C Master mode and SPI Slave mode cannot be used at the same time.</li> <li>I2C and SPI can be used as Master at the same time only when specific GPIO pins are configured as I2C and SPI pins, respectively. Please refer to corresponding SDK.</li> </ul> |

| 14  | UART                         | <ul> <li>♦ Embed UART to implement full-duplex transmission and reception.</li> <li>♦ ANA_C&lt;6&gt;/ANA_C&lt;7&gt; can be configured as TX/RX to communicate with other device via UART.</li> <li>♦ Support hardware flow control when ANA_D&lt;0&gt;/ANA_D&lt;1&gt; or ANA_E&lt;6&gt;/ANA_F&lt;0&gt; are configured as RTS and CTS pins.</li> </ul>                                                                                                                                                                                                                                                                                     |

| 15  | Analog microphone<br>(AMIC)  | <ul> <li>♦ Support AMIC input.</li> <li>♦ Adopt single-end input: use ANA_C&lt;0&gt;/ANA_C&lt;1&gt; as<br/>AmicBias/AmicIn.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 16  | Digital microphone<br>(DMIC) | <ul> <li>♦ Support DMIC input.</li> <li>♦ Use ANA_E&lt;1&gt;/ANA_E&lt;2&gt; as DMIC_CLK/DMIC_DI.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| No. | ltem                           | Description                                                                                                                                                                         |

|-----|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17  | Audio output<br>(SDM)          | <ul> <li>♦ Support mono-channel audio output.</li> <li>♦ Use ANA_E&lt;4&gt;/ANA_E&lt;5&gt; as SDM_P/SDM_N.</li> </ul>                                                               |

| 18  | ADC                            | ♦ ADC input channel: ANA_C<2>~ANA_C<7>, ANA_D<0>~ANA_D<5>.                                                                                                                          |

| 19  | Battery detect                 | <ul> <li>◇ It's needed to use one ADC input channel to detect battery voltage.</li> <li>◇ It's needed to connect external divider resistor for all power supply methods.</li> </ul> |

| 20  | TLSR8266F512<br>pin connection | For TLSR8266F512 QFN32 package, it's needed to connect PIN3 with PIN8.<br>For TLSR8266F512 QFN48 package, it's needed to connect PIN3 with PIN12.                                   |

# 3.2 Schematic design guide

| No. | ltem                                                       | Description                                                                                                                                                                                                                                                                                                                                               |

|-----|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VDDDEC                                                     | ♦ VDDDEC should be connected to GND via 1uF filtering capacitor.                                                                                                                                                                                                                                                                                          |

| 2   | DVDD, AVDD                                                 | Both DVDD and AVDD pin should be connected with a 1uF decoupling capacitor.                                                                                                                                                                                                                                                                               |

| 3   | Reset pin                                                  | ♦ RST pin should be connected to GND via 1uF capacitor.                                                                                                                                                                                                                                                                                                   |

| 4   | Crystal oscillator                                         | <ul> <li>◇ It's recommended to use 12MHz crystal with spec of<br/>12MHz-12pF-+/-20ppm.</li> <li>◇ Load capacitors are reserved for crystal pins (not soldered by<br/>default).</li> </ul>                                                                                                                                                                 |

| 5   | Test points for FW<br>burning and<br>wakeup source         | <ul> <li>◇ It's needed to reserve three test points including VCC, GND and<br/>SWS for firmware burning.</li> <li>◇ According to test plan, it's needed to reserve a GPIO test point as<br/>wakeup source for sleep/wakeup test. It's recommended to use<br/>ANA_C&lt;2&gt; as wakeup source corresponding to Telink standard test<br/>script.</li> </ul> |

| 6   | BQB certificate<br>&<br>FCC RF certificate                 | <ul> <li>It's needed to reserve TX/RX test points for BLE BQB certificate test.</li> <li>FCC RF certificate matching location: It's needed to reserve π-type low pass filtering circuit for ANT pin in order to decrease RF harmonic energy. Default parameters: 2.2nH series inductor, two 1.5pF shunt capacitors.</li> </ul>                            |

| 7   | Antenna                                                    | <ul> <li>◇ Telink solution uses monopole PCB antenna.</li> <li>◇ It's needed to reserve a shunt device matching location near the antenna port for antenna match debug.</li> </ul>                                                                                                                                                                        |

| 8   | Does default state<br>of PB0/PD4/PD5<br>influence circuit? | <ul> <li>By default ANA_B&lt;0&gt; and ANA_D&lt;4&gt; output high level, and<br/>ANA_D&lt;5&gt; outputs low level. If any of the three IOs is used in circuit<br/>design, please take its default state into consideration.</li> </ul>                                                                                                                    |

| 9   | USB                                                        | <ul> <li>For USB dongle applications, it's needed to connect a 33Ω series<br/>resistor between the DP/DM pin and the USB port, and the resistor<br/>should be close to the USB port.</li> </ul>                                                                                                                                                           |

| 10  | TLSR8266F512/F128<br>power supply                          | <ul> <li>◇ For TLSR8266F512/F128, its internal Flash won't work if its power supply drops below 2.7V.</li> <li>◇ Consider using Li battery or four AAA dry batteries, and then use LDO step-down circuit to supply power for system.</li> <li>◇ If Li battery is used, please reserve system reset circuit for miniUSB interface.</li> </ul>              |

# 4 TLSR8263 Hardware Design Guide

#### 4.1 Hardware functions

| No. | ltem                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Package                       | ♦ Support QFN24, TSSOP16 and ESOP8L package.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2   | Program memory<br>(OTP/Flash) | <ul> <li>♦ Embed 16KB OTP.</li> <li>♦ TLSR8263ET24 supports external 128/512KB Flash.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3   | Swire                         | <ul> <li>♦ Support Single Wire Slave (SWS) interface.</li> <li>♦ 8263 (Slave) can communicate with SWM of Master via SWS.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4   | GPIO                          | <ul> <li>◇ TLSR8263ET24 supports up to 14 GPIOs.</li> <li>◇ TLSR8236ES16 supports up to 9 GPIOs.</li> <li>◇ TLSR8263EP8 supports up to 3 GPIOs.</li> <li>◇ All digital IOs (including MSDO/MSDI/MSCN/MSCK) can be configured as GPIOs.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5   | Wakeup source                 | <ol> <li>TLSR8263ET24:</li> <li>GP17~GP18, GP22~GP23 and GP31 can be configured as active-high or active-low Pad wakeup sources.</li> <li>GP17~GP18 wakeup polarity is configured at the same time.</li> <li>Wakeup polarity of GP22~GP23 and GP31 is independently configurable.</li> <li>TLSR8263ES16:</li> <li>GP17~GP18 and GP22~GP23 can be configured as active-high or active-low Pad wakeup sources.</li> <li>GP17~GP18 wakeup polarity is configured at the same time.</li> <li>Wakeup polarity of GP22~GP23 can be configured as active-high or active-low Pad wakeup sources.</li> <li>GP17~GP18 wakeup polarity is configured at the same time.</li> <li>Wakeup polarity of GP22~GP23 is independently configurable.</li> <li>TLSR8263EP8:</li> <li>GP17 can be configured as active-high or active-low Pad wakeup source.</li> </ol> |

| 6   | Pull-up/Pull-down<br>resistor | <ul> <li>1. TLSR8263ET24:</li> <li>         GP17~GP18, GP22~GP23 and GP31 support independently configurable<br/>10KΩ/1MΩ pull-up resistor or 100KΩ pull-down resistor.</li> <li>         GP5 and GP9~GP10 support independently configurable 100KΩ<br/>pull-down resistor.</li> <li>         By default the pull-up and pull-down resistors are disabled.     </li> <li>         TLSR8263ES16:</li> <li>         GP17~GP18 and GP22~GP23 support independently configurable<br/>10KΩ/1MΩ pull-up resistor or 100KΩ pull-down resistor.     </li> </ul>                                                                                                                                                                                                                                                                                           |

| No. | ltem             | Description                                                                                        |

|-----|------------------|----------------------------------------------------------------------------------------------------|

|     |                  | pull-down resistor.                                                                                |

|     |                  | $\diamond$ By default the pull-up and pull-down resistors are disabled.                            |

|     |                  | 3. TLSR8263EP8:                                                                                    |

|     |                  | $\Leftrightarrow$ GP17 supports configurable 10KΩ/1MΩ pull-up resistor or 100KΩ                    |

|     |                  | pull-down resistor.                                                                                |

|     |                  | $\Leftrightarrow$ GP5 supports configurable 100KΩ pull-down resistor.                              |

|     |                  | ♦ MCLK/MSDO/MSDI/MSCN: maximum=4mA ("DS"=1), minimum=2mA                                           |

|     |                  | ("DS"=0).                                                                                          |

|     |                  | $\Rightarrow$ SWS: maximum=8mA ("DS"=1), minimum=4mA ("DS"=0).                                     |

| 7   | Driving strength | $\diamond$ Other GPIO pins support maximum drive level of 4mA ("DS"=1) and                         |

|     | (DS)             | minimum drive level of 0.7mA ("DS"=0).                                                             |

|     |                  | $\diamond$ The "DS" configuration will take effect when the pin is used as output,                 |

|     |                  | and it's set as the strongest driving level by default.                                            |

|     |                  | ♦ Support 4-channel PWM output: PWM0~PWM3. PWM#n_INV indicates                                     |

|     |                  | inverted output.                                                                                   |

| 8   | PWM              | ♦ PWM0 supports two modes: continuous mode, counting mode.                                         |

|     |                  | ♦ PWM1~PWM3 only support continuous mode.                                                          |

|     |                  | ♦ IR driving is not supported.                                                                     |

|     |                  | ♦ Embed I2C hardware module.                                                                       |

|     |                  | ♦ Only support Slave mode. SCL should be configured as input.                                      |

|     |                  |                                                                                                    |

|     |                  | 1. TLSR8263ET24:                                                                                   |

|     |                  | $\Leftrightarrow$ GP22/GP23 can be configured as SCL/SDA, and internal 10KΩ pull-up                |

|     |                  | resistor can be used.                                                                              |

|     |                  | ♦ GP30/PG31 can be configured as SCL/SDA, and it's needed to connect<br>outcomed will up resistor. |

| 9   | I2C              | <ul> <li>external pull-up resistor.</li> <li>♦ GP5 can't be configured as SDA.</li> </ul>          |

| 9   | 120              | Y GPS can't be configured as SDA.                                                                  |

|     |                  | 2. TLSR8263ES16:                                                                                   |

|     |                  | <ul> <li>◇ GP4/GP5 can be configured as SCL/SDA, and it's needed to connect</li> </ul>             |

|     |                  | external pull-up resistor.                                                                         |

|     |                  | $\Rightarrow$ GP22/GP23 can be configured as SCL/SDA, and internal 10K $\Omega$ pull-up            |

|     |                  | resistor can be used.                                                                              |

|     |                  |                                                                                                    |

|     |                  | 3. TLSR8263EP8 does not support I2C interface.                                                     |

|     |                  | ♦ Support 4 ADC input channels via G17/G18/G22/G23 pin.                                            |

| 10  | ADC              | ♦ Except for G23 with internal divider resistors, other ADC input pin                              |

| _   |                  | should be connected with external 1/3 divider resistors.                                           |

|     |                  |                                                                                                    |

| No. | ltem           | Description                                                                                                          |

|-----|----------------|----------------------------------------------------------------------------------------------------------------------|

| 11  | Battery detect | Use G23 with internal 1/3 divider resistors as battery detect pin, so that no external divider resistors are needed. |

# 4.2 Schematic design guide

| No. | ltem                                               | Description                                                                                                                                                                                                                                                                                                                                                    |

|-----|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VDDDEC                                             | ♦ VDDDEC should be connected to GND via 1uF filtering capacitor.                                                                                                                                                                                                                                                                                               |

| 2   | DVDD, AVDD                                         | Both DVDD and AVDD pin should be connected with a 1uF decoupling capacitor.                                                                                                                                                                                                                                                                                    |

| 3   | Reset pin                                          | ♦ RST pin should be connected to GND via 1uF capacitor.                                                                                                                                                                                                                                                                                                        |

| 4   | Test points for FW<br>burning and<br>wakeup source | <ul> <li>◇ It's needed to reserve four test points including VCC, GND, SWS and VPP for OTP burning.</li> <li>◇ According to test plan, it's needed to reserve a GPIO test point as wakeup source for sleep/wakeup test. It's recommended to use GP17 as wakeup source corresponding to Telink standard test script.</li> </ul>                                 |

| 5   | BQB certificate<br>&<br>FCC RF certificate         | <ul> <li>It's needed to reserve three test points including SDA, SCL and one GPIO for BLE BQB certificate test.</li> <li>FCC RF certificate matching location: It's needed to reserve π-type low pass filtering circuit for ANT pin in order to decrease RF harmonic energy. Default parameters: 2.2nH series inductor, two 1.5pF shunt capacitors.</li> </ul> |

| 6   | Antenna                                            | <ul> <li>Telink solution uses monopole PCB antenna.</li> <li>It's needed to reserve a shunt device matching location near the antenna port for antenna match debug.</li> </ul>                                                                                                                                                                                 |

| 7   | ROW/COL                                            | <ul> <li>For remote control applications:</li> <li>◇ ROW pins should be selected as IOs with internal pull-up resistor.</li> <li>◇ COL pins should be selected as IOs with internal pull-down resistor.</li> <li>◇ If COL pins are selected as MSDO/MSDI/MSCN/MCLK, it's needed to connect external 100K pull-down resistor.</li> </ul>                        |

| 8   | EEPROM                                             | <ul> <li>In remote control applications, OTP is used for burning, and<br/>EEPROM should be reserved to store user information.</li> </ul>                                                                                                                                                                                                                      |

| 9   | Battery detect                                     | Use G23 as battery detect pin, and no external divider resistors are needed for 3V power supply.                                                                                                                                                                                                                                                               |

| 10  | VPP                                                | $\diamond$ VPP should be supplied with external 6.75V power for OTP burning.                                                                                                                                                                                                                                                                                   |

# 5 General PCB Design Rules

| No. | General PCB design rules                                                                                                                                                                                                                               |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | <ul> <li>Decoupling capacitors of chip power pins should be placed close to the power<br/>pins.</li> </ul>                                                                                                                                             |  |

| 2   | <ul> <li>Filtering capacitors of VDDDEC and DVDD3F should be placed close to the VDDDEC<br/>and DVDD3F pin.</li> </ul>                                                                                                                                 |  |

|     | <ul> <li>Keep the antenna 5mm (or above) away from metal devices (e.g. metal screw, metal board frame).</li> <li>The figure below shows a bad design example: Antenna design is close to USB connector.</li> </ul>                                     |  |

| 3   |                                                                                                                                                                                                                                                        |  |

| 4   | <ul> <li>Since battery would largely influence antenna Tx/Rx performance, keep the<br/>antenna 3~5mm (or above) away from the battery.</li> </ul>                                                                                                      |  |

| 5   | Antenna trace width shouldn't be too narrow in order to decrease loss; line width should be 0.5mm or above, generally it's recommended to be 0.5mm or 1mm.                                                                                             |  |

| 6   | <ul> <li>Top and bottom of antenna location should not be covered by GND.</li> <li>The distance between antenna and GND should be 3mm or above.</li> </ul>                                                                                             |  |

| 7   | ♦ Generally antenna length is 20~40mm. The smaller the GND is, the longer the antenna should be.                                                                                                                                                       |  |

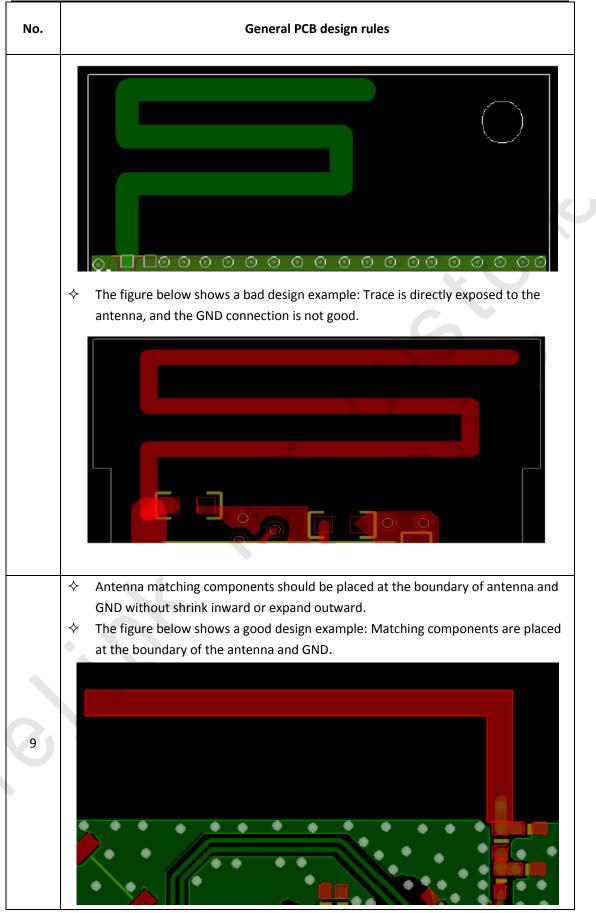

| 8   | <ul> <li>There should be a row of via holes along the antenna on the side parallel to GND.</li> <li>Do not directly expose trace or pad to the antenna.</li> <li>The figure below shows a good design example: Via holes are placed evenly.</li> </ul> |  |

AN-16101000-E1

| No. | General PCB design rules                                                                                                                                                                                                      |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | The figure below shows a bad design example: Matching components shrink inward the GND.                                                                                                                                       |

|     |                                                                                                                                                                                                                               |

|     |                                                                                                                                                                                                                               |

|     | <ul> <li>Place the π-type filtering device of RF close to the RF pin.</li> <li>The RF line to the antenna port should be short. If the RF line is not short enough, it must be designed as 50ohm micro-strip line.</li> </ul> |

|     | <ul> <li>There should be even via holes along the RF line, and the ground plane should be integral.</li> <li>The figure below shows a good design example: The π-type filtering device is</li> </ul>                          |

|     | placed close to the RF pin.                                                                                                                                                                                                   |

| No. | General PCB design rules                                                                                                                                                                                                                                                                                                                                                         |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

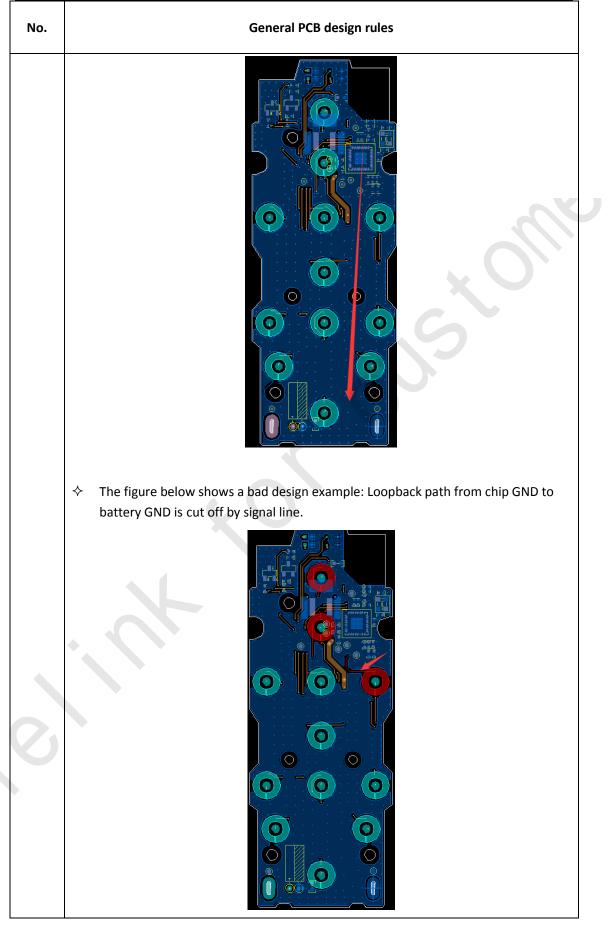

|     | $\Rightarrow$ The figure below shows a bad design example: The π-type filtering device is placed away from the RF pin.                                                                                                                                                                                                                                                           |

|     |                                                                                                                                                                                                                                                                                                                                                                                  |

| 11  | <ul> <li>Power line should be as thick and short as possible.</li> <li>Generally width of power line is 0.5mm~0.6mm.</li> </ul>                                                                                                                                                                                                                                                  |

| 12  | <ul> <li>If power line is not short enough, consider using 0.8mm (or above) width.</li> <li>Ground current should have wide and fluent loopback path from RF GND to chip GND, then to power GND. Try to keep the integrity of ground plane.</li> <li>The figure below shows a good design example: Loopback path is wide from RF GND to chip GND then to battery GND.</li> </ul> |

Г

| No. | General PCB design rules                                                                                                                                                                 |  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 13  | $\diamond$ Ground loopback should return to battery after filtered by LDO capacitor.                                                                                                     |  |

| 14  | <ul> <li>To avoid mutual interference, modules such as crystal oscillator, Audio, Mic and<br/>USB should be isolated with GND and protected by via holes as much as possible.</li> </ul> |  |

| 15  | For modules such as Audio, Mic and USB, it's better to keep the integrity of ground plane without division.                                                                              |  |

| 16  | <ul> <li>For audio applications, it's needed to adopt star-type connection for power in<br/>order to decrease noise caused by dirty power.</li> </ul>                                    |  |