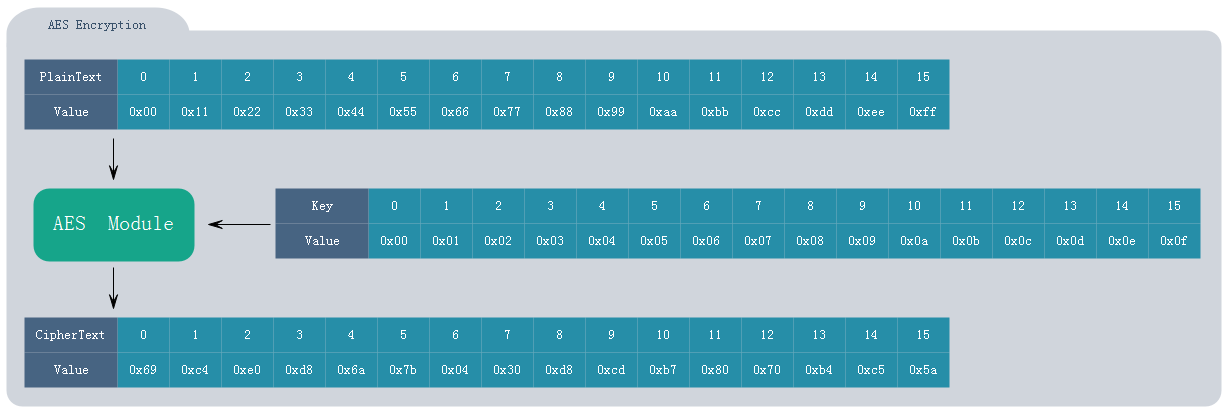

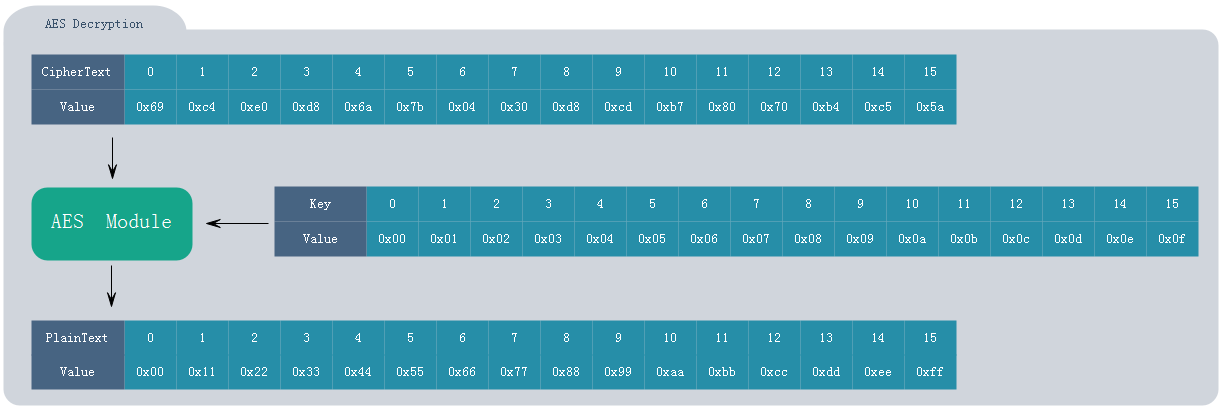

The TLSR8258F512 embeds AES module with encryption and decryption function.The input 128bit plaintext in combination of key is converted into the final output ciphertext via encryption;the 128bit ciphertext in combination of key can also be converted into 128bit plaintext via decrytion.

The AES hardware accelerator provides automatic encryption and decryption. It only takes 1000 x System clock cycles to implement AES encryption or decryption. Suppose system clock is 20MHz, the time needed for AES encryption or decryption is 50us.

Both RISC mode and DMA mode are supported for AES operation.

The RISC mode essentially uses a state machine to encrypt and decrypt data. It should be noted that RISC mode only supports 128bit(16bytes) encryption and decryption. The registers involved are mainly divided into 4 categories, as shown below:

| Category | Register | Description |

|---|---|---|

| REG_AES_KEY0 - REG_AES_KEY15 | 0x550-0x55f | set value of key, A total of 16 bytes |

| REG_AES_CTRL | 0x540[0] | set operation method of AES module:1-decryption,0-encryption |

| 0x540[1] | automatically clear after quartic writing of address 0x548-0x54b | |

| 0x540[2] | Be automatically set as 1 after encryption or decryption operation and then cleared automatically after quartic reading of address 0x548-0x54b | |

| REG_AES_DAT0 - REG_AES_DAT3 | 0x548-0x54b | write registers for 4 times to set the 128bit plaintext or read registers for 4 times to get the 128bit ciphertext |

The encryption process is shown below:

The decryption process is shown below:

AES module supports DMA mode, which can greatly simplify data encryption and decryption process. Besides, parallelism between DMA and MCU can improve the efficiency of the program. To use the DMA mode, in addition to the relevant configuration, the data structure sent must follow the specific requirements below:

In order to facilitate users to quickly develop products according to their own needs, TSI provide the following related APIs and examples.

| APIs list | Description | Example | Update Date | Status |

|---|---|---|---|---|

| aes_encrypt() | AES encryption operation in RISC mode | API-AES-CASE1 | 2019-1-10 | Done |

| aes_decrypt() | AES decryption operation in RISC mode | API-AES-CASE1 | 2019-1-10 | Done |

| aes_dma_encrypt() | AES encryption operation in DMA mode | API-AES-CASE2 | 2019-1-10 | Done |

| aes_dma_decrypt() | AES decryption operation in DMA mode | API-AES-CASE2 | 2019-1-10 | Done |

TSI provides the following examples of this module to help users quickly understand and apply related modules.

| Examples list | Description | Update Date | Status |

|---|---|---|---|

| API-AES-CASE1 | encrypt and decrypt in RISC mode | 2019-1-10 | Done |

| API-AES-CASE2 | encrypt and decrypt in DMAmode | 2019-1-10 | Done |

| Date | Description | Author |

|---|---|---|

| 2019-1-10 | initial release | LJW |